創意、愛普 啖先進封裝商機

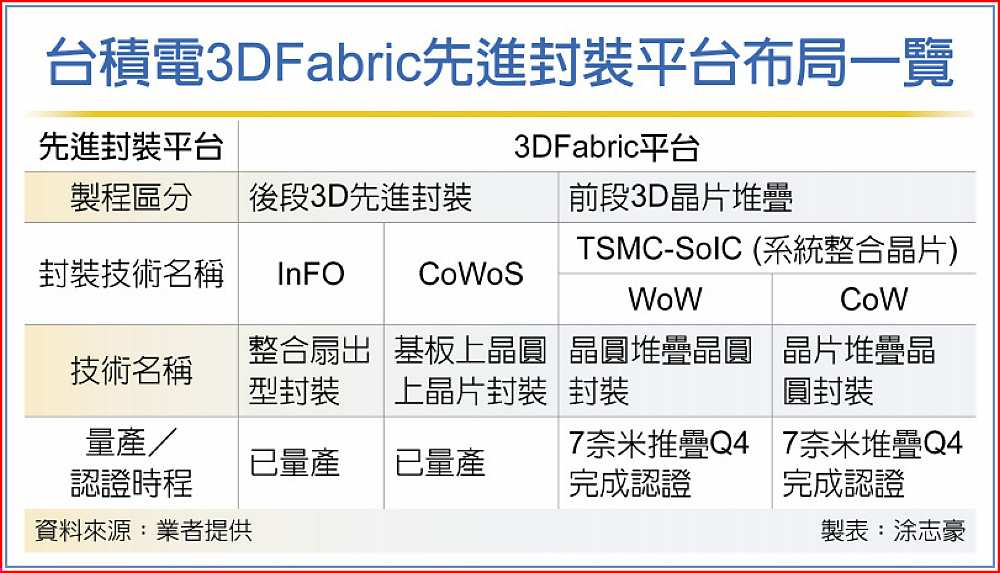

小晶片(chiplets)或晶片塊(tiles)等新一代異質晶片設計架構,推動人工智慧及高效能運算(AI/HPC)應用成長爆發,將不同異質晶片整合為單一晶片的先進封裝技術成為市場新顯學。台積電今年加強InFO及CoWoS等2.5D先進封裝產能布建及製程推進,3DFabric先進封裝平台開始進入生產階段,合作夥伴創意(3443)及愛普(6531)同步受惠。

包括英特爾、超微、輝達、博通等業者透過小晶片或晶片塊的設計架構,搭配高頻寬記憶體(HBM)或特殊型DRAM,已可針對不同的AI及HPC應用量身打造運算效能強大的加速器或處理器。然而要將邏輯運算核心串接並與記憶體整合為單一晶片,只能透過先進封裝技術來達成,台積電加速3DIC先進封裝技術推進並整合到3DFabric平台,第四季將完成7奈米製程晶圓或晶片的堆疊封裝技術認證。

台積電去年將先進封裝技術整合到3DFabric平台,包括前段3D矽堆疊技術TSMC-SoIC,以及包括CoWoS與InFO的後段導線連結技術所組成,提供客戶整合異質小晶片的彈性解決方案。其中,台積電第五代CoWoS先進封裝將在年底前推出,採用小晶片設計架構的多晶片模組(MCM)繪圖晶片將採用台積電技術,超微Aldebaran繪圖處理器率先採用,輝達Hopper繪圖處理器將在明年量產。

台積電轉投資IC設計服務廠創意近年來積極爭取AI及HPC處理器的委託設計(NRE)開案,搭配台積電CoWoS或SoIC等先進封裝技術,已爭取到國際大廠訂單。創意也推出可在CoWoS上擴充組合多個系統單晶片(SoC)及HBM3記憶體的GLink 2.5D介面,以及支援台積電3DFabric先進封裝技術的GLink 3D晶粒堆疊晶粒(DoD)介面矽智財,能堆疊組裝不同的晶粒組合以滿足不同市場區隔需求。

由於HBM記憶體價格昂貴,愛普推出全新DRAM介面的異質整合高頻寬記憶體(VHM)技術,包含客製化DRAM設計、DRAM與邏輯晶片整合介面VHM LInK IP,由力積電提供客製化DRAM晶圓代工,並採用台積電WoW先進封裝製程,下半年已經進入量產。其中,鯨鏈科技採用此一方案量產挖礦專用特殊應用晶片(ASIC),後續包括Google的TPU、豪威的CMOS影像感測器均將會採用。