世芯破傳言 再購台積光罩

向台積電取得8.34億元光罩,間接證明今年出貨將如預期、不受影響

股王世芯-KY(3661)21日公告向台積電(2330)取得2,621萬美元之機器設備,約合新台幣8.34億元。世芯財務長王德善證實,即是向晶圓代工廠購置光罩。

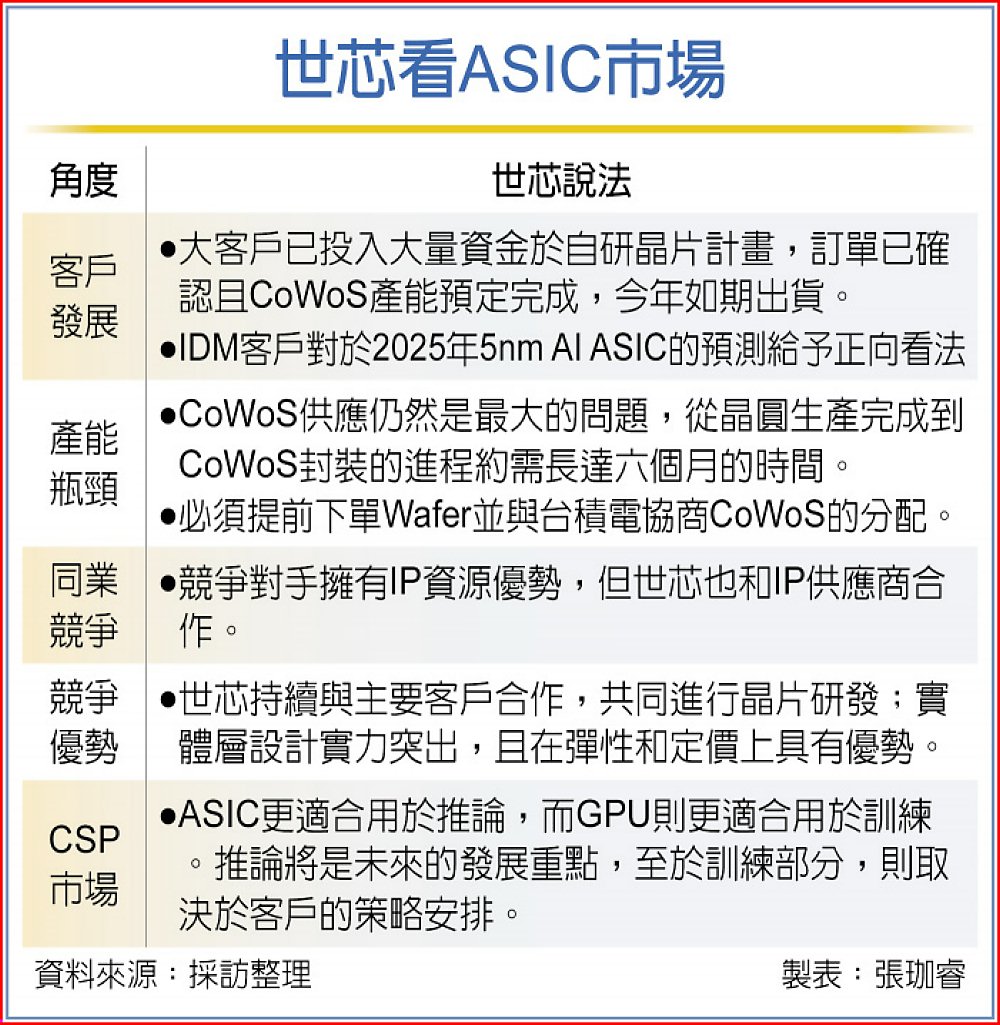

世芯表示,CoWoS產能供應依舊吃緊,但公司目前在台積電Wafer/CoWoS用量漸具份量,去年已一舉躍升至第四大CoWoS用戶;惟世芯也強調,不單是晶圓廠的支持,本身更具備大量先進製程後段設計經驗,長期仍將與客戶保持密切合作。

為破除市場傳言,世芯以行動證實最大客戶並未放棄自研晶片。世芯強調,客戶已投入大量資金於自研晶片計畫,同時訂單已確認,並且在台積電之CoWoS產能也預定完成;王德善分析,為確保先進封裝的順利進行,必須提前下單Wafer(晶圓)並與台積電協商CoWoS產能分配,而先進封裝產能依舊吃緊,現在放棄就必須重新排隊。

王德善強調,從晶圓生產完成到CoWoS封裝的進程約需長達六個月的時間;AI發展爭分奪秒,尤其CSP業者算力即是競爭力,在購買通用型GPU的同時,進行自研晶片開發,訓練、推論雙線進行。

世芯更認為,推論應用將是未來的發展重點,其中,ASIC特別適合用於推論。

關於競爭對手來勢洶洶,世芯具信心地表示,將持續與主要客戶合作,共同進行晶片研發。競爭對手同樣擁有IP資源等優勢,不過世芯也會與IP供應商合作,能夠在三個月內提供相當的高速傳輸介面IP,且實體設計更是世芯拿手,在彈性和定價上具備優勢。

外界傳CSP業者將收回部分自研ASIC。世芯認為,在人力資源有限下,應會優先投入資源在前段設計,世芯作為後段設計業者,尤其擅長台積電製程的實體設計,特別是在2.5/3D先進封裝、chiplet、I/O die、HBM等高度複雜的架構。

針對明年展望,王德善分享北美IDM客戶對於明年5nm(奈米)AI ASIC預測,已給予正向看法,另外,明年亦有陸系車用晶片將導入,持續保持樂觀態度。